Differences between use of CISC and RISC processors.

Complex Instruction Set Computer (CISC):

This type of processor attempts to reduce the number of instructions per program, however meaning the number of cycles per instruction is increased and hardware complexity is increased as it needs to understand more complex instructions. CISC architecture is designed to decrease the use of memory as memory is very expensive. It does this by shortening down instructions so less RAM is required to store instructions. This means that a CPU can perform complex tasks with one instruction. E.g: MULT 2:3, 5:2.

Reduced Instruction Set Computer (RISC):

These processors can only support small, simple instructions which can be completed in a single clock cycle. This means that more complex instructions need to be split up into multiple lines of instructions to perform a task. E.g: The MULT 2:3, 5:2 from CISC needs to be represented like this for a RISC processor.

LOAD A, 2:3

LOAD B, 5:2

PROD A, B

STORE 2:3, A

Pipelining:

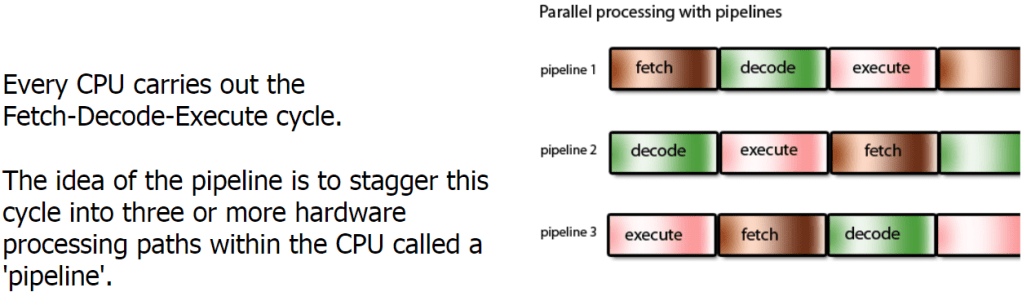

Pipelining is when the CPU processes more than one piece of data simultaneously. Processes can “overlap”. Multiple instructions are overlapped in execution.

The benefit of pipelining is to increase throughput but without decreasing latency.

Throughput: Rate at which tasks are completed.

Latency: The time it takes to complete a single task.

Pipelining did not reduce completion time for one task but it helps throughput of the entire workload in turn decreasing the completion time.